无线基站曾经封装在采用气候控制技术的大型空间中,但现在却可以装在任意地方。随着无线网络服务提供商试图实现全域信号覆盖,基站组件提供商面临压力,需要在更小的封装中提供更多的功能。

来自ADI公司的一对集成电路(IC)提供了一种解决方案,重新界定了接收器前端混频器的意义。实际上,该IC在混频器IC内部集成了曾经附加于接收器内混频器的许多组件,比如,本振(LO)和中频(IF)放大器。利用这些IC,可以大幅减少蜂窝基站的大小,同时还能带来软件定义无线电(SDR)的灵活性,从而应对多种不同的无线标准。

这里涉及的IC的型号是ADRF6612和ADRF6614,根据设计二者支持的RF范围为700 Mhz至3000 MHz,LO范围为200 Mhz至2700 MHz,IF范围为40 Mhz至500 MHz。它们支持低端或高端LO注入,包括一个板载锁相环(PLL)和多个低噪声电压控制振荡器(VCO),全部封装在7 mm × 7 mm 48引脚的LFCSP外壳中。超高的集成度和组件密度,加上多样性和可编程能力,可以支持多种不同的无线标准,完全满足现代微蜂窝的小批量生产需求。

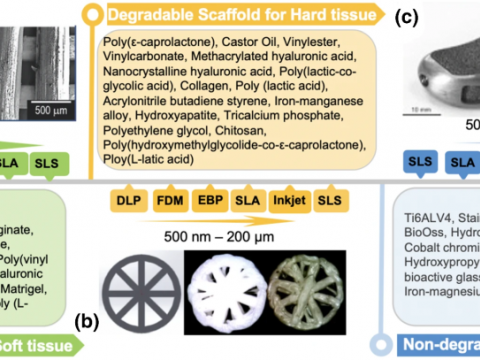

为了更好地理解这些高度集成的混频器IC在节省空间方面的优势,不妨回忆一下2010年左右时的蜂窝基站的前端,如图1所示。双混频器架构的带宽范围约为1 Ghz,需要多个组件来处理当时的蜂窝频率范围,即800 MHz至1900 MHz。频率合成由一个独立的PLL和窄带VCO模块提供,需要用一个特有的PLL环路滤波器才能实现最佳性能。每个目标频段均采用专门的VCO模块,结果增加了基站内需要的电路板面积。

另外,这些分立式组件是通过低阻抗传输线路相互连接起来的,结果会增加信号损失。结果,需要很大的电流把VCO输出驱动到足够的电平,以便混频器能在信号阻塞条件下产生低相位噪声和噪声系数。

集成VCO的接收器IC并非新事物。但要实现多载波要求的宽带宽和低相位噪声,全球移动通信系统(MC-GSM)无线网络一直是个挑战。GSM的信道复用方案要求接收LO具有极低的相位噪声,尤其是在相间通道失调频率为800 kHz的情况下,如图2所示。如果这些相间通道的多余相位噪声与同样处于800 kHz失调条件下的无用信号相混合,则可能使相位噪声转换成IF输出,从而降低系统的灵敏度。

图1.框图所示为2010左右时的典型蜂窝基站

图2.信道复用方案要求在GSM无线系统中采用低相位噪声的宽带宽VCO,避免因阻塞导致性能下降

低VCO相位噪声通常是通过高质量因数(高Q)谐振器和窄带设计实现的。频分也能降低噪声。通过使VCO工作于接收器LO频率的整数倍,随后进行的分频即可使相位噪声降低一个6 dB/倍频程,如图3所示。GSM在1800 Mhz至1900 Mhz频段内的相位噪声要求极高,其严重程度大约相当于800 Mhz至900 Mhz频段内相位噪声的两倍。

图3.该VCO电路配置可实现倍频程带宽

在低相位噪声以外,现代基站接收器设计必须支持无线通信网络当前使用的多种调制方案。除GSM以外,其他调制方案包括宽带码分多址(WCDMA)和长期演进(LTE)系统。接收器设计通常包括若干不同的VCO,其相位噪声性能配置为中等水平,通过组合的方式满足基站倍频程带宽需求。

一旦将若干个VCO配置为在最高工作频率下产生一个倍频程带宽,则可用二分频实现较低的LO频率。ADRF6612接收器混频器采用的就是这种方法,其中,VCO基频范围为2.7 Ghz至5.6 Ghz,通过从1至32分频,两级频分实现200 Ghz至2700 Mhz的LO频率。对于同时包括MC-GSM的应用,ADRF6614接收器混频器包括两个额外的高性能VCO内核,用于提供1800 Mhz至1900 MHz GSM频段所需要的LO频率。

由于现代无线微蜂窝可能不具备气候控制环境的优势,所以这些接收器IC一类的组件可在较宽的极限温度范围内提供一致、可靠的性能。为了在较宽的工作温度范围内实现规定的性能,ADRF6612和ADRF6614 IC中的PLL和VCO采用了多种校准技术。

对于低噪声宽带宽,每个VCO内核采用一个8位的容性数模转换器(CDAC),后者可以为给定的LO频率选择正确的频段(128选1)。系统会仔细监控VCO谐振器幅度的任何变化,并用自动电平控制(ALC)系统调整幅度,以获得最佳输出幅度。每个IC都会在工作频率被重新编程的时候执行校准序列。这样可以确保所选频段将VCO调谐变容二极管的调谐电压集中于最佳范围内,使频率合成器在所需工作温度范围保持锁定。

每个ADRF6612和ADRF6614 IC中的四个VCO内核可以确保其工作范围具有合适的重叠性,能适应不同的环境条件和器件制造容差。对于环境和工艺差异,内核一般会以相同的方向移动频率,因而内建了充足的重叠机制,使得频率合成器能够始终实现锁定条件。

一旦确定校准方案,就可以无限地维持频率,调谐电压范围支持需要的同步范围。在时分双工(TDD)系统中,基站可能根据不同的时隙改变频率,其工作时间可能按微秒计。在频分双工(FDD)系统中,可能需要多年锁定单个频率。

在ADRF6612和ADRF6614 IC系统工作期间,任何时候都不允许出现故障停机事故。因此,温度变化和组件老化效应通过VCO的变容调谐电压范围和频率调谐灵敏度(kV)来处理,温度范围有可能达145°C。每个IC会根据需要持续监控器件温度并调整VCO偏置。

ADRF6612和ADRF6614 Ic采用一种独特方法,最大限度地减轻由杂散信号产物导致的接收器灵敏度下降问题。利用频率合成器的整数模式和紧凑环路滤波器可使参考杂散产物低至−100 dBc以下。最小杂散信号对调制方案至关重要,如MC-GSM。对于LTE和其他调制方案,或者在需要精细的频率阶跃的情况下,频率合成器可以工作于小数N分频模式。参考路径集成一个13位分频器,整数和小数路径各自集成16位分频器,具有极大的灵活性。

对于需要共置相位跟踪接收通道的应用中,如多输入多输出(MIMO)系统,可以通过菊花链方式将ADRF6612和ADRF6614 IC级联起来,以便允许其中一个单元作为主频率合成器,分别通过其外部LO输出和输入端口为其他从机接收器供电。这样,就可以最大限度地降低额外LO分配放大器及其相位噪声相应增大的程度。

为了同时支持高端和低端LO注入,每个IC的LO链提供了灵活的信号处理,如图4所示。使用1至32的整数分频比,即使是700 Mhz频段和高IF,也可实现低端注入。LO级在从200 Mhz至2700 Mhz的整个LO范围内,同时为无源混频器内核提供一个方波驱动。1

图4.本LO信号链用于支持无线基站接收器

现代无线基站带内信号在频率上接近低电平输入信号,因而蜂窝接收器可以充当阻塞信号。在这种情况下,在目标信号之上,来自阻塞信号附近LO放大器的相位噪声被混频进IF输出频段。这样会提高噪底,有时能大幅降低接收器的信噪比(SNR)。

由于阻塞信号可能较大(高功率),所以VCO相位噪声必须极低,并且LO链不会在阻塞器失调条件下降低噪底。在这些超高的阻塞电平下,接收器噪声系数会最终被阻塞信号主导,并根据阻塞器功率水平的高低下降。

在分立式接收链方案中,可以在LO路径上引入一些滤波机制,以在阻塞器失调条件下,最大限度地降低来自VCO和LO分配放大器的相位噪声。然而,在集成式前端中,必须谨慎,避免LO链中的加性相位噪声。

ADRF6612和ADRF6614 IC采用高增益LO链和硬限幅放大器以将LO链驱动至限幅。当每个级进入硬限幅时,在其他情况下会增大相位噪声的LO链小信号增益将大幅下降,从而将阻塞条件下的噪声系数下降问题减至最低。

来自阻塞信号的噪声折叠会降低接收器输出噪声频谱性能,提高输出噪底,从而降低接收器噪声系数。根据设计,ADRF6612和ADRF6614接收器IC可在最大限度减小接收器噪声系数降幅的条件下承受较大的阻塞信号,如图5所示。即使输入阻塞电平为10 dBm,在载波失调10 MHz条件下,接收器的噪声系数也只会下降3.2 dB,即使转换增益在极端阻塞电平下缩减1 dB,亦是如此。

这些接收器IC具有超高的集成度,因而对现代无线基站设计师来说,可以大幅提升性能,节省DC功耗,如图6所示。IC采用一种技术,可以同时优化片上混频器周围的RF和IF级。2

该技术首次用于ADRF6612,在整个温度范围内和整个频率范围内以及低功耗条件下,最低IIP3超过25 dBm,在整个温度范围内,为29 dBm至2 GHz。该技术还具有最佳接收路径噪声系数性能和高转换增益,如图7所示。3,4

图5.本图比较了ADRF6614接收器IC在低电平和高电平阻塞信号(分别为左侧和右侧)下的输出噪声频谱

图6.本信号链所示为典型无线基站接收器中采用的组件

图7.图中所示为ADRF6612接收器IC的实测增益、噪声系数和输入三阶交调截点(IIP3)。

致谢

随着完整接收器链内在集成度的提高,开发团队的规模也大幅增加。虽然这里无法列出为本文做出贡献的全体人员,但本文作者非常荣幸地向下列行业专家表示由衷的谢意:Kurt Fletcher和Dominic Mai花了大量时间以实现优秀的布局并保持对称,避免无用耦合。Vincent Bu与我们的供应商密切配合,开发必要的封装。Susan Stevens与外部代工合作伙伴维持了良好的工作关系。Craig Levy和Rachana Kaza为这些器件开发了生产测试功能。Wendy Dutile、Ed Gorzynski和Chris Norcross都参与了测试电路的大量原型制作工作。Mark Hyslip负责业务协调,使得本项目得以成型。本文作者希望以本文纪念我们的同事,Edward J. Gorzynski。

参考文献

1 Marc Goldfarb, Russel Martin, and Ed Balboni.“Novel Topology Supports Wideband Passive Mixers.”(新型拓扑结构支持宽带无源混频器)Microwaves & RF,第90页,2011年10月。

2 Marc Goldfarb.“Apparatus and Method for a Wideband RF Mixer.”(宽带RF混频器装置和方法)ADI公司,2012年。

ADRF6612数据手册。ADI公司,2016。

ADRF6614数据手册。ADI公司,2016。

about the Authors

作者简介

Tom Bosia [thomas.bosia@analog.com] joined ADI in 2013 as an RF product engineer. Prior to Analog Devices, he was an RF test engineer at Raytheon, Cree, and Auriga Microwave, accruing over 25 years of experience in microwave semiconductors. He received a B.S.E.E. from UMass Lowell in 2001.

Tom Bosia [thomas.bosia@analog.com]于2013年加盟ADI公司,担任RF产品工程师。加盟ADI公司之前,在Raytheon、Cree和Auriga Microwave等公司担任RF测试工程师,在微波半导体领域积累了超过25年的经验。2001年获得麻省大学罗威尔分校电气工程学士学位。

Russell Martin [russell.martin@analog.com] joined ADI in 2002 and had 15 years of experience releasing IC products to market as a product engineer before becoming engineering manager in the RF and Microwave Group (RFMG). He graduated from Worcester Polytechnic Institute in 2002 with a B.S.E.E.

Russell Martin [russell.martin@analog.com]于2002年加盟ADI公司,任产品工程师,负责IC产品的市场发布工作达15年;后来成为ADI公司RF和微波部门(RFMG)的工程经理。2002年毕业于伍斯特理工学院,获电气工程学士学位。

Marc Goldfarb [marc.goldfarb@analog.com] has over 35 years of design experience in analog, RF, and microwave integrated circuits in military, industrial, and consumer applications. He has worked in SiGe/silicon, GaAs, and microwave hybrid integrated circuit technologies, among others. Prior to joining Analog Devices, Marc held engineering roles at Pacific Communications Sciences, Inc. (PCSI), Raytheon, and M/A-COM Microwave Associates. He holds a Master of Engineering degree from Rensselaer Polytechnic Institute in Troy, NY, has 13 patents, and has authored numerous publications for reference and trade journals.

Marc Goldfarb [marc.goldfarb@analog.com]在模拟、RF和微波集成电路领域拥有超过35年的设计经验,涉及军事、工业和消费电子等应用。他曾从事过SiGe/硅、GaAs和微波混合集成电路技术等工作。加盟ADI公司之前,Marc曾在Pacific Communications Sciences, Inc. (PCSI)、Raytheon和M/A-COM Microwave Associates公司工作,历任多个工程职位。他毕业于纽约特洛伊伦斯勒理工学院,获工程硕士学位;获13项专利,在参考类资料和行业期刊上发表论文多篇。

Marc is a design engineer with the RF and Microwave Group (RFMG) focused on the development of RF ICs for the wireless infrastructure and is presently leading the design team for a series of 5th generation communications infrastructure (5G IC) projects.

Marc目前是RF和微波部门(RFMG)的一名设计工程师,主要负责无线基础设施RF IC开发工作;目前担任多个5G通信基础设施(5G IC)项目的设计组组长。

Dragoslav Culum [dragoslav.culum@analog.com] is a product line manager at Analog Devices. He has over 10 years of experience in wireless communications. Dragoslav joined Analog Devices in 2014 through the Hittite acquisition. He joined Hittite in 2008 and since then has held various positions including applications engineer, marketing engineer, and product line manager in a number of product lines. Dragoslav obtained his Bachelor of Engineering from McMaster University and a Master of Engineering from Carleton University.

Dragoslav Culum [dragoslav.culum@analog.com]是ADI公司的产品线经理。他在无线通信领域拥有超过10的工作经验。2014年,在Hittite并购完成后,Dragoslav加盟ADI。他于2008年加盟Hittite,并历任多个职位,包括应用工程师、营销工程师和多个产品系列的产品线经理。Dragoslav分别从麦克马斯特大学和卡尔顿大学获工程学士学位和工程硕士学位。

Ben Walker [benjamin.walker@analog.com] received his Bachelor of Engineering and Master of Engineering degrees from the Massachusetts Institute of Technology, in 2003 and 2004, respectively. Since 2004, he has worked for Analog Devices, Inc., in the RF and Microwave Group on a variety of circuits for the wireless infrastructure market. Ben’s interests include phase-locked loops, voltage-controlled oscillators, and RF switch and attenuator design.

Ben Walker [benjamin.walker@analog.com]于2003年和2004年分别获得麻省理工学院的工程学士学位和工程硕士学位。2004年以来,他一直在ADI公司RF和微波部门工作,参与了面向无线基础设施市场的多种电路设计工作。Ben的兴趣包括锁相环、电压控制振荡器和RF开关及衰减器设计。

Ed Balboni [ed.balboni@analog.com] has 30 years’ experience designing high performance, highly integrated, radio transceiver circuits. His expertise is in microwave, RF, mixed-signal, and analog circuits in SiGe BiCMOS, bipolar, and CMOS technologies for communication products. Ed joined Analog Devices in 2000 and works in the RF IC Design Group as an IC designer and design manager. At ADI he develops high performance RF IC components supporting wireless infrastructure including cellular base stations and point-to-point microwave.

Ed Balboni [ed.balboni@analog.com]在高性能、高集成度无线电收发器电路设计领域拥有30年经验。他擅长基于SiGe BiCMOS、双极性和CMOS技术设计面向通信产品的微波、RF、混合信号和模拟电路。Ed于2000年加盟ADI公司,在RF IC设计部门担任IC设计师和设计经理。他在ADI负责开发支持无线基础设施的高性能RF IC组件,包括蜂窝基站和点对点微波。

Prior to joining ADI, Ed worked at Draper Laboratory in Cambridge, MA on MEMS inertial sensors and low power communication electronics. Ed graduated from University of Massachusetts Lowell with a B.S.E.E. degree in 1985 and received a M.S.E.E. degree in 1990 from Northeastern University.

加盟ADI之前,Ed曾在麻省剑桥的Draper实验室工作,负责MEMS惯性传感器和低功耗通信电子元器件的设计。Ed 1985年毕业于麻省大学洛威尔分校,获电气工程学士学位,1990年毕业于东北大学,获电气工程硕士学位。

(采编:www.znzbw.cn)

经营性网站备案信息

经营性网站备案信息 ICP经营许可证

ICP经营许可证 营业执照副本

营业执照副本 不良信息举报中心

不良信息举报中心